时序电路的设计

用移位寄存器设计时序电路

04年真题

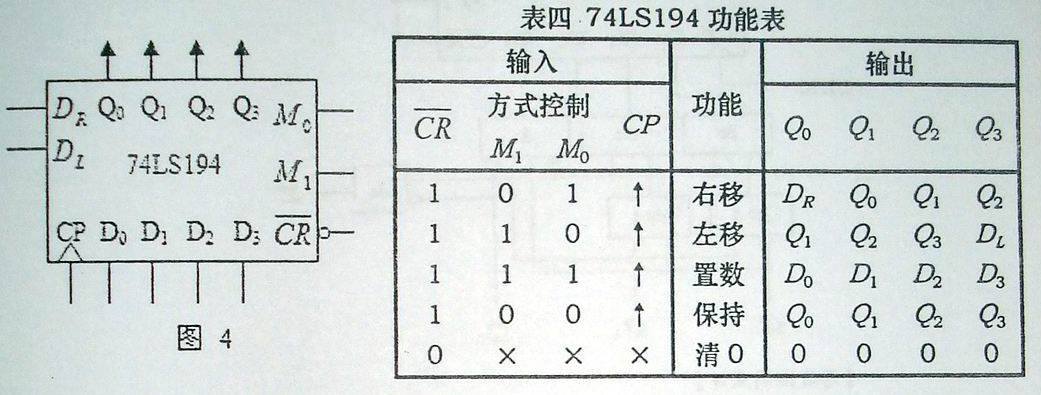

采用一片双向移位寄存器74LS194及其它必要的器件设计一个状态图如下图所示的控制器。

思路:

①. 观察状态图,提出几个过程:

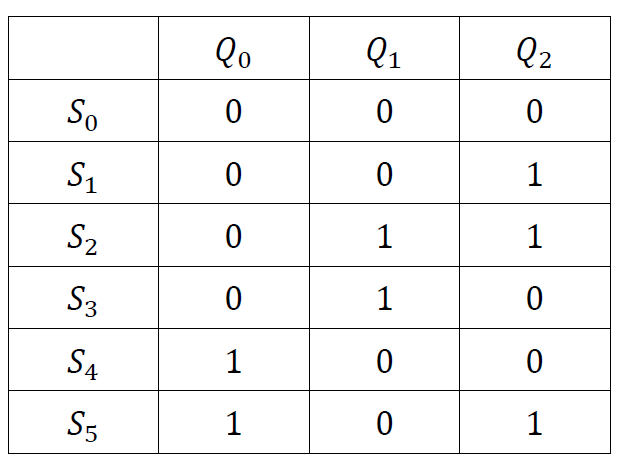

②. 为了设计方便,状态编码可为:

③. 把所有的状态编码通过3-8线译码器解码,解码输出的信号会有用到:

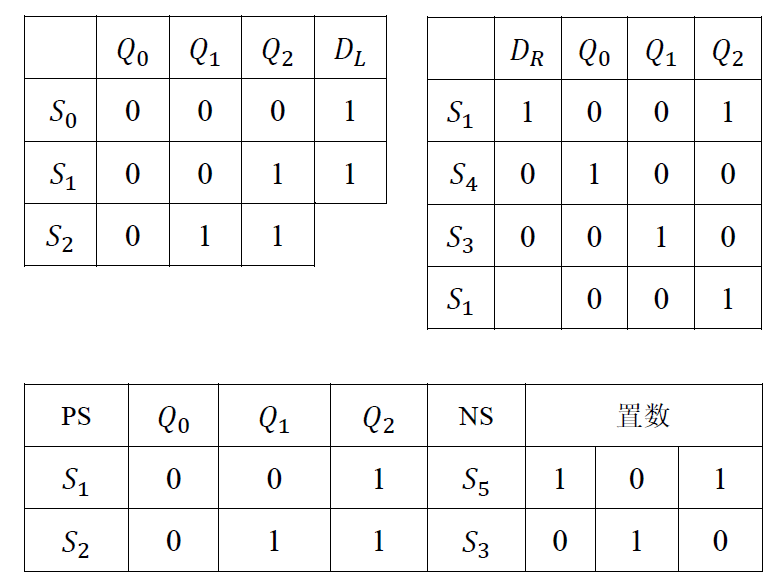

④. 这样编码的条件下,状态图在双向移位寄存器中可以表现成如下图所示:

观察上图可以得出逻辑电路的连接方式:

- $S_0\to S_1\to S_2$:$Q_0$反接$D_L$,左移

- $S_1\to S_4\to S_3\to S_1$:$Q_2$接$D_R$,右移

- $S_1\to S_5\quad S_2\to S_3$:置数。当$S_2$状态时,译码器输出的$S_2=1$,下个状态需要置数$010$;当$S_3$状态时,译码器输出的$S_2=0$,下个状态需要置数$101$;故可以将所置数据为$Q_0Q_1Q_2=\bar S_2S_2\bar S_2$。(同理也可以是$S_3\bar S_3S_3$)

故相关的状态方程可表示为:

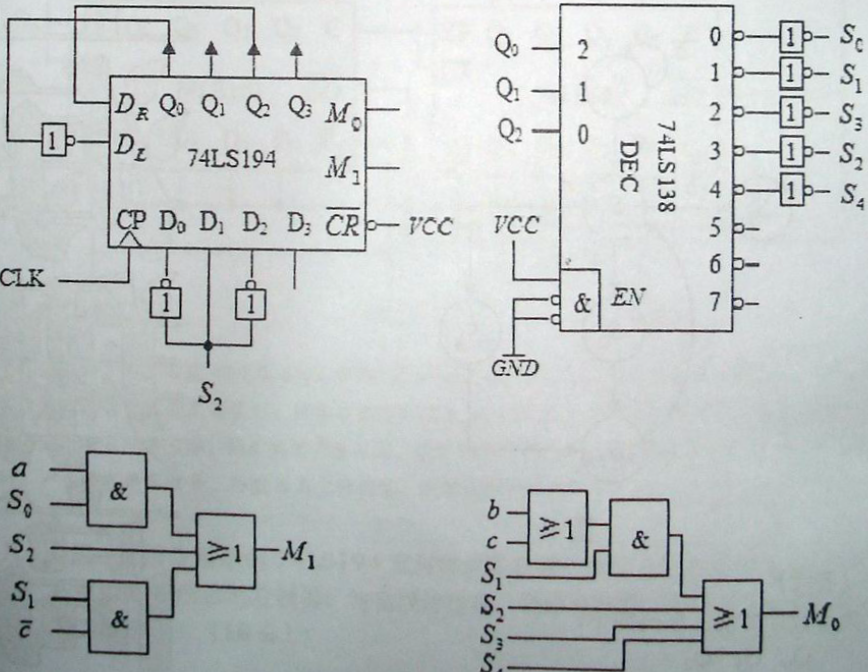

⑤. 最终的逻辑电路图如下:

07年真题

十二、利用双向移位寄存器及其它必要的器件设计控制器时序状态电路。

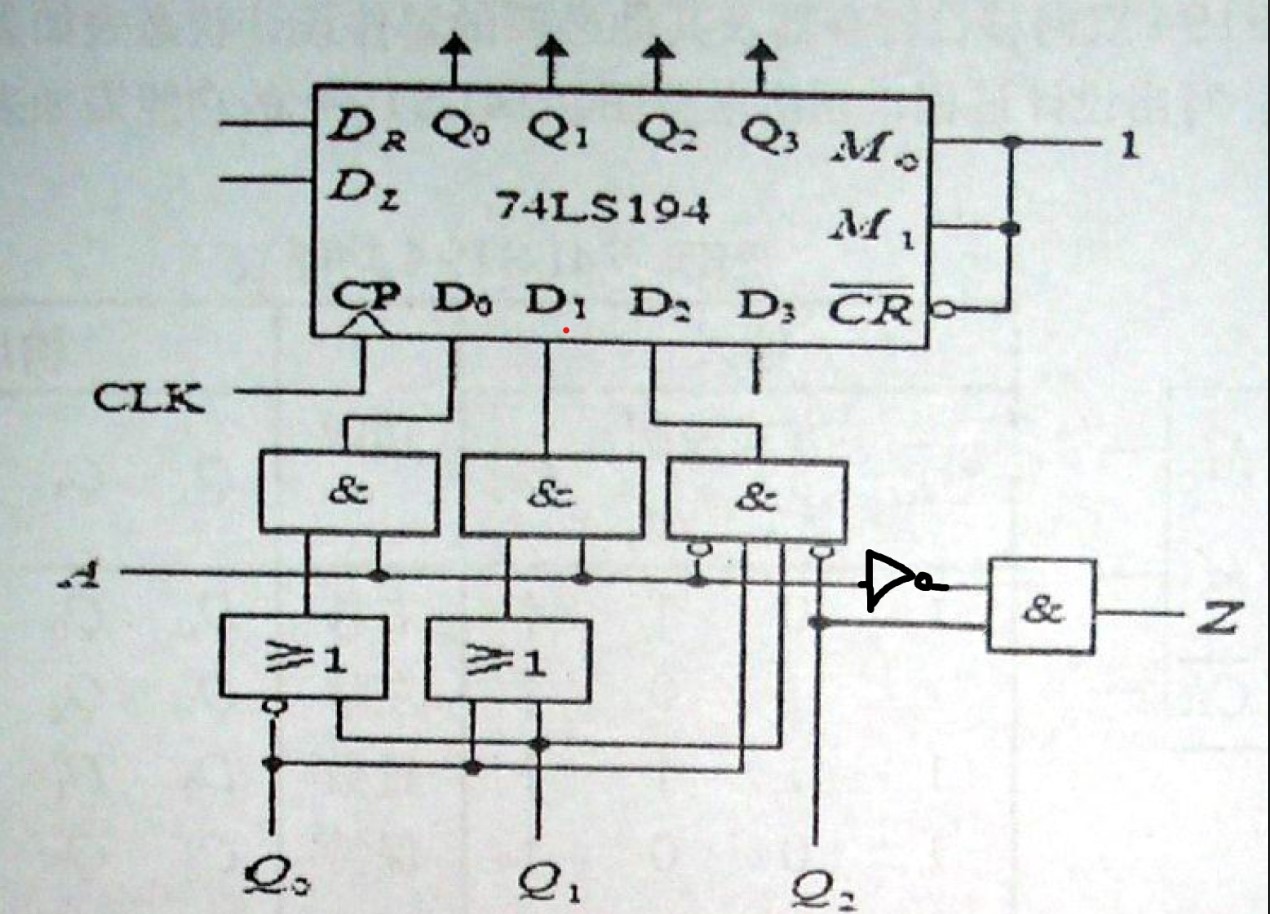

思路:观察状态表可得,当$A=0$或$1$时都令移位寄存器置数比较方便:

当$A=0$时,令移位寄存器置数,$M_1M_0=11$,$D_2=Q_2’Q_1Q_0$,$D_1=0$,$D_0=0$,$Z=Q_2$

当$A=1$时,令移位寄存器置数,$M_1M_0=11$,$D_2=0$,$D_1=Q_1+Q_0$,$D_1=Q_1+Q_0’$,$Z=0$

故综上得:

所以电路为:

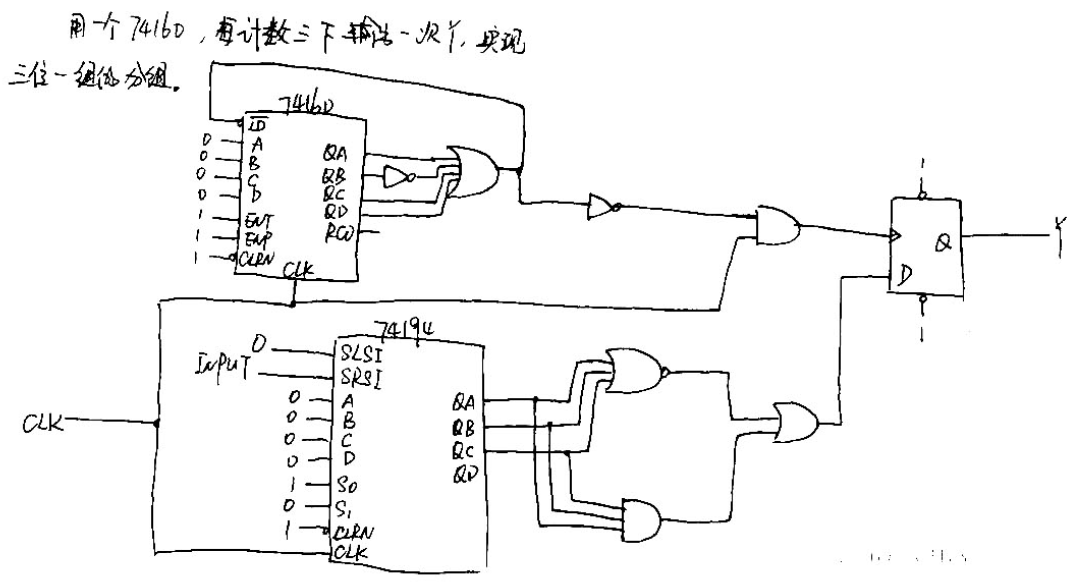

11年真题

八、用双向移位寄存器及必要器件设计一个三位一组的分组码检测电路,当检测到分组码为000或111时,输出Y为1,否则为0。画出状态转换图,写出设计过程,画出电路图。

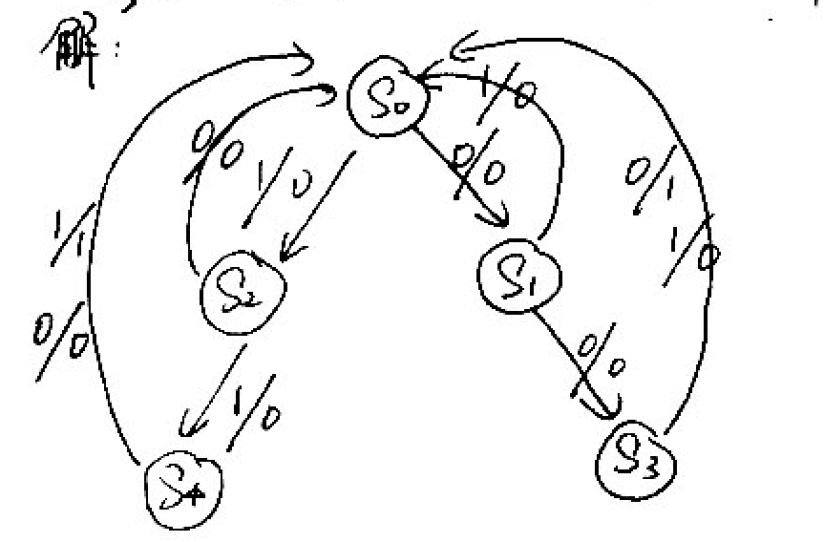

思路:

①. 设计状态:$S_0$: 是连续输入0个0和0个1时的状态;$S_1$: 是连续输入1个0时的状态;$S_2$:连续输入1个1时的状态;$S_3$:连续输入2个0时的状态;$S_4$:连续输入2个1时的状态。画状态转换图:

②. 设计电路:注意,因为是三位一组,所以采用计数器74160设计为3进制计数器,每计数3下输出一次$Y$。

13年真题

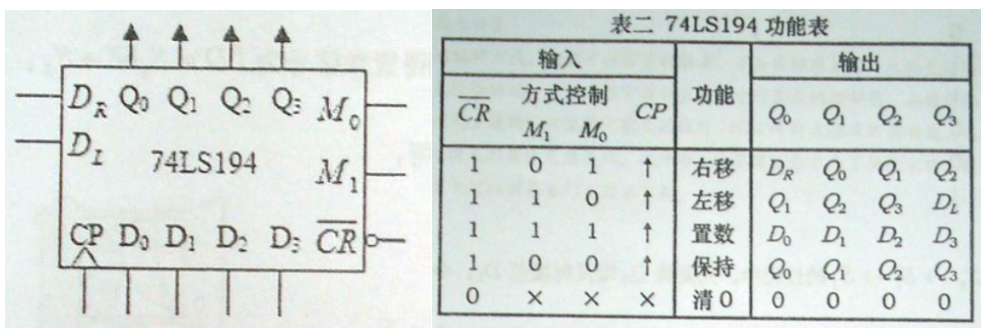

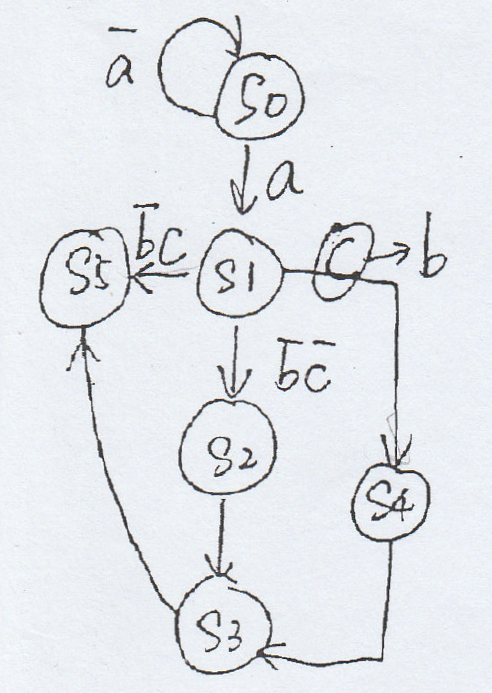

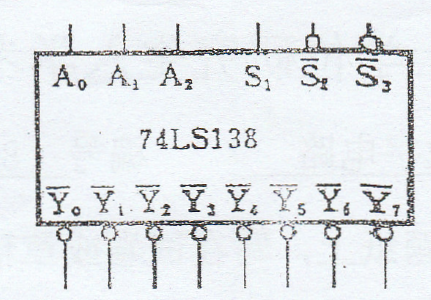

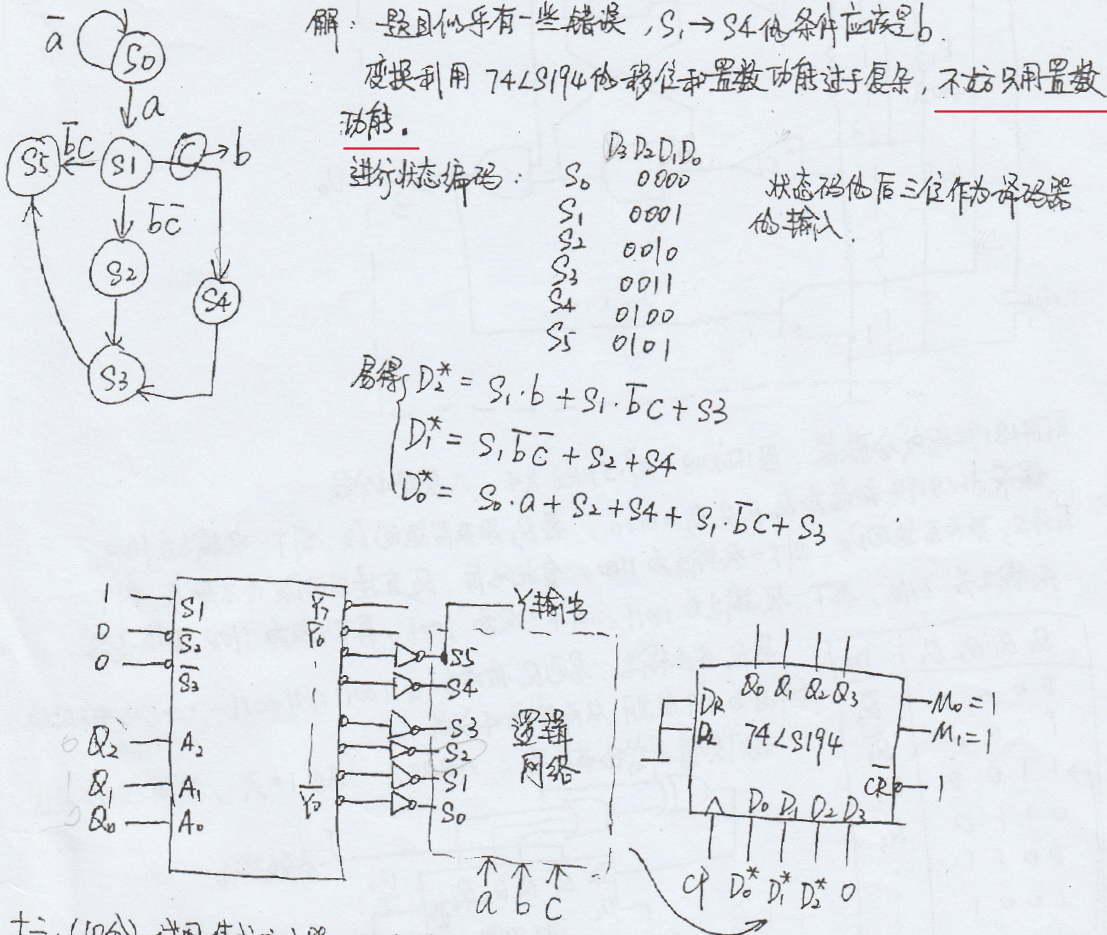

十一、用74LS194双向移位寄存器及3线/8线译码器74LS138为主要器件设计一个状态图吐下的控制器。其中a,b,c为输入信号,控制器在状态S5时有一个输出信号$Y=1$。

思路:可以根据04年真题来做,但是会比较复杂,答案里全部用的是置数功能。

用计数器设计时序电路

以计数器为核心设计控制器的原理在于利用输入信号以及当前状态来控制计数器进行计数、保持、置数或者清零等操作。

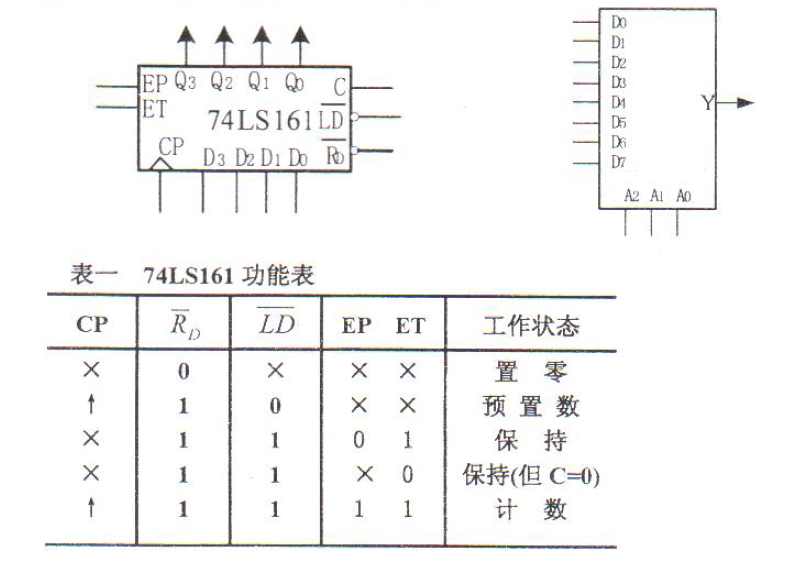

06年真题

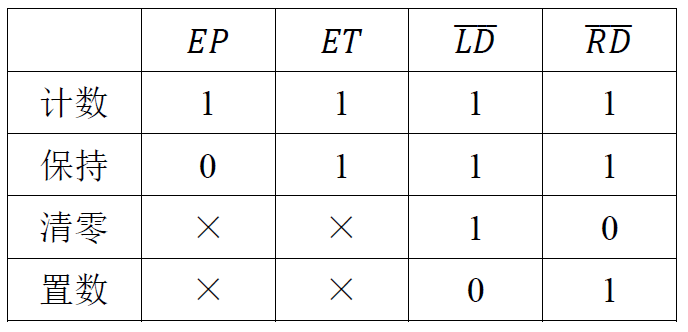

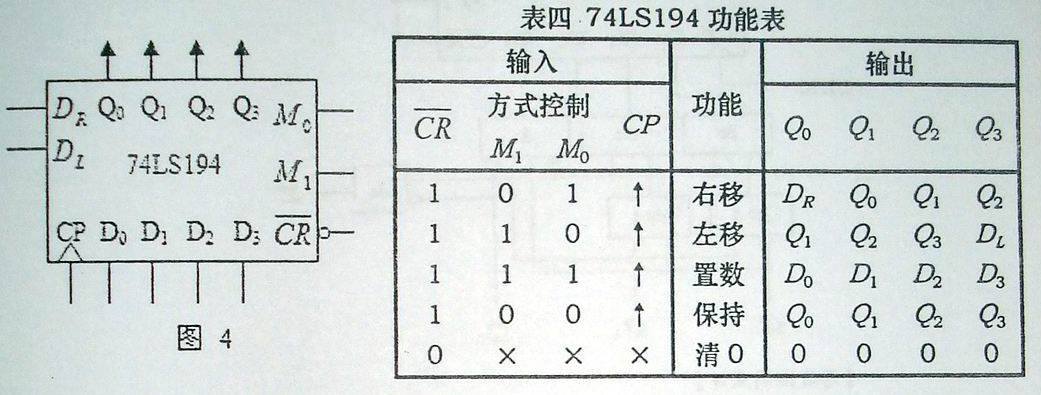

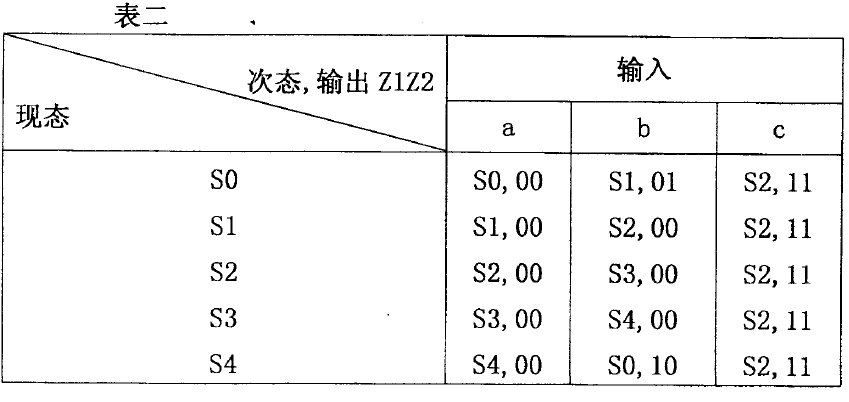

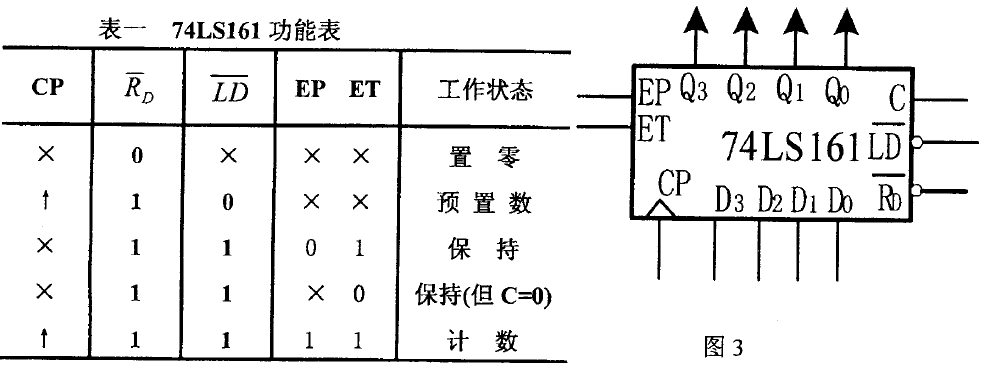

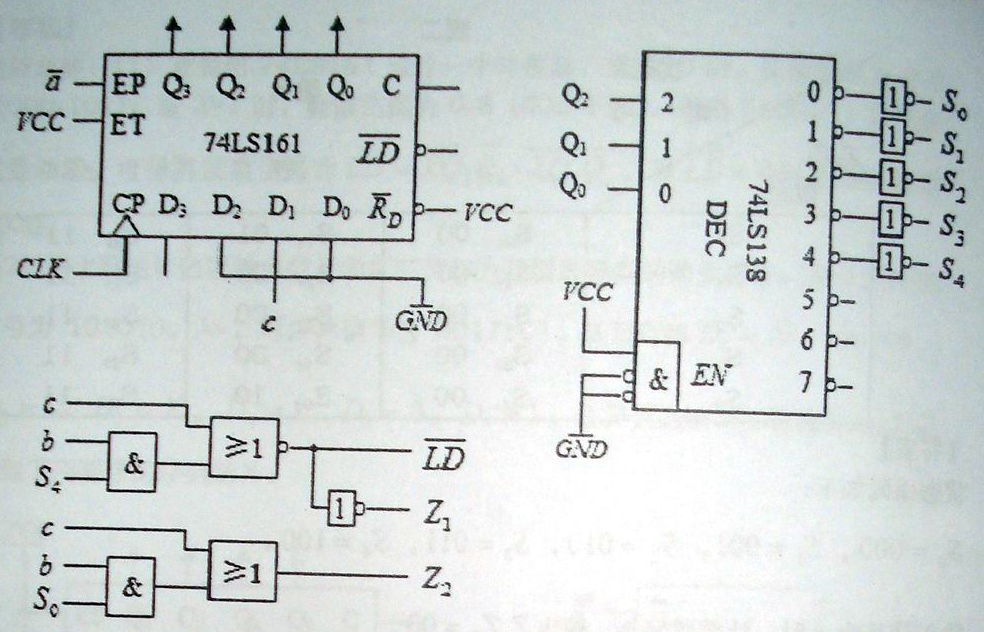

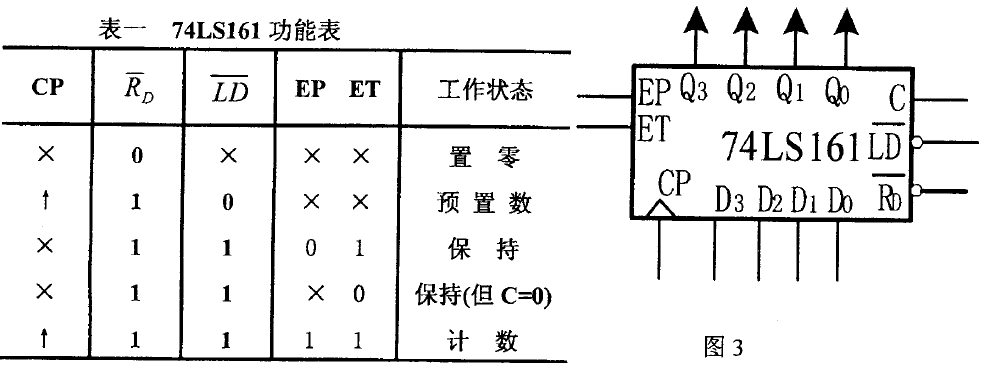

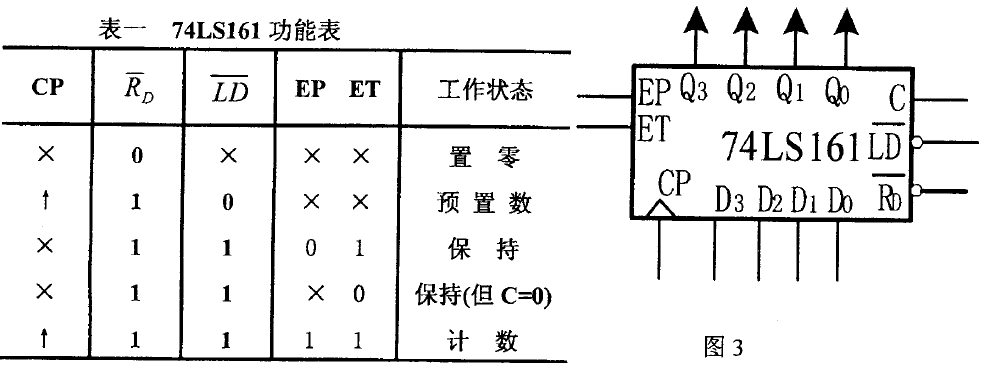

十、以 一个16进制计数器74161为核心和其它必要的器件设计如状态表所示的控制器。

思路:

①. 状态编码:$S_0=000,S_1=001,S_2=010,S_3=011,S_4=100$。

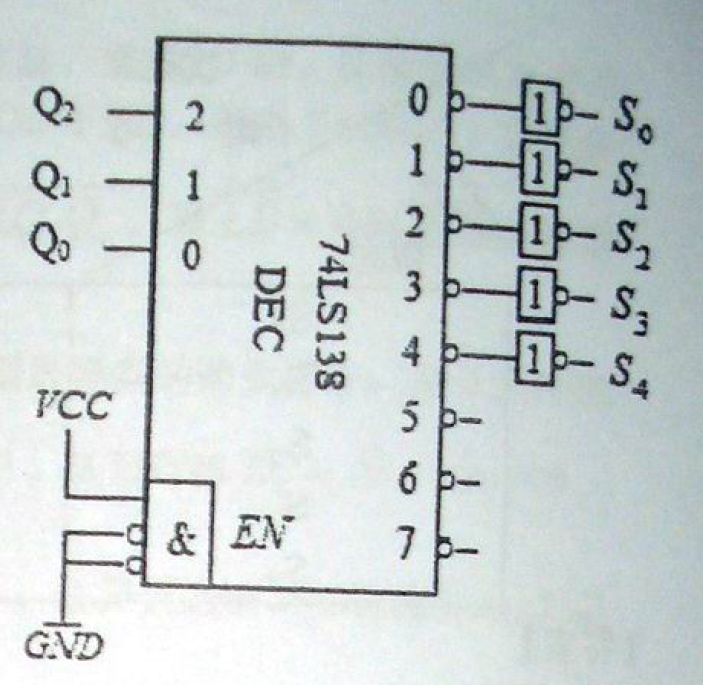

②. 用3线-8线译码器进行状态解码,这要每个状态都可由单独的$S_0\sim S_4$信号表示。即状态为$S_2$就可以直接表示成$S_2=1$。

②. 分析:

- 输入信号为$a$时,状态不变,故计数器保持,输出$Z_1Z_2=0$;

- 输入信号为$b$时,状态前进一位,故计数器计数,输出$Z_1=S_4,Z_2=S_1$;当计数器计数至$100$,重新置数$000$;

- 输入信号为$c$时,状态置为$S_2$,故计数器置数$010$,输出$Z_1Z_2=11$。

所以可得:

- $EP=\bar a$——输入信号为$a$时计数器保持;

- $D_2=0,D_1=c,D_0=0,\overline{LD}=\overline{bS_4+c}$——当输入信号为$b$且计数至$100(S_4)$时置数$000$,当输入信号为$c$时置数$010$;

- $Z_1=bS_4+c,Z_2=bS_1+c$

故电路图为:

08年真题

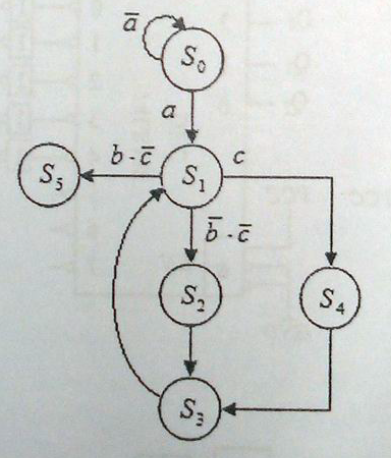

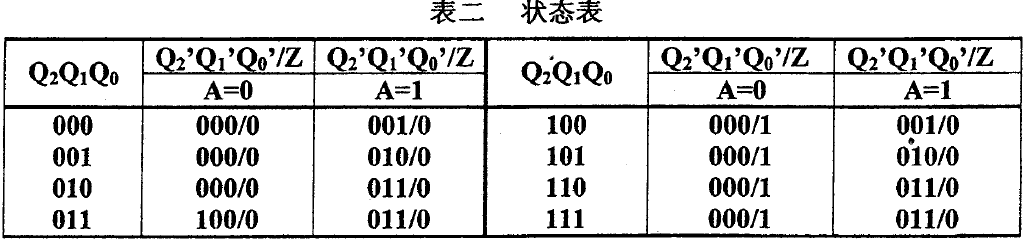

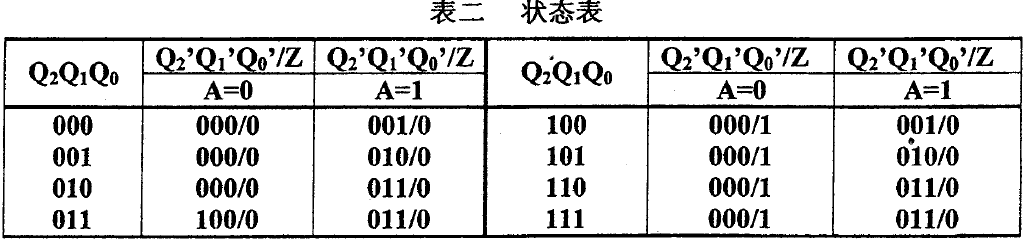

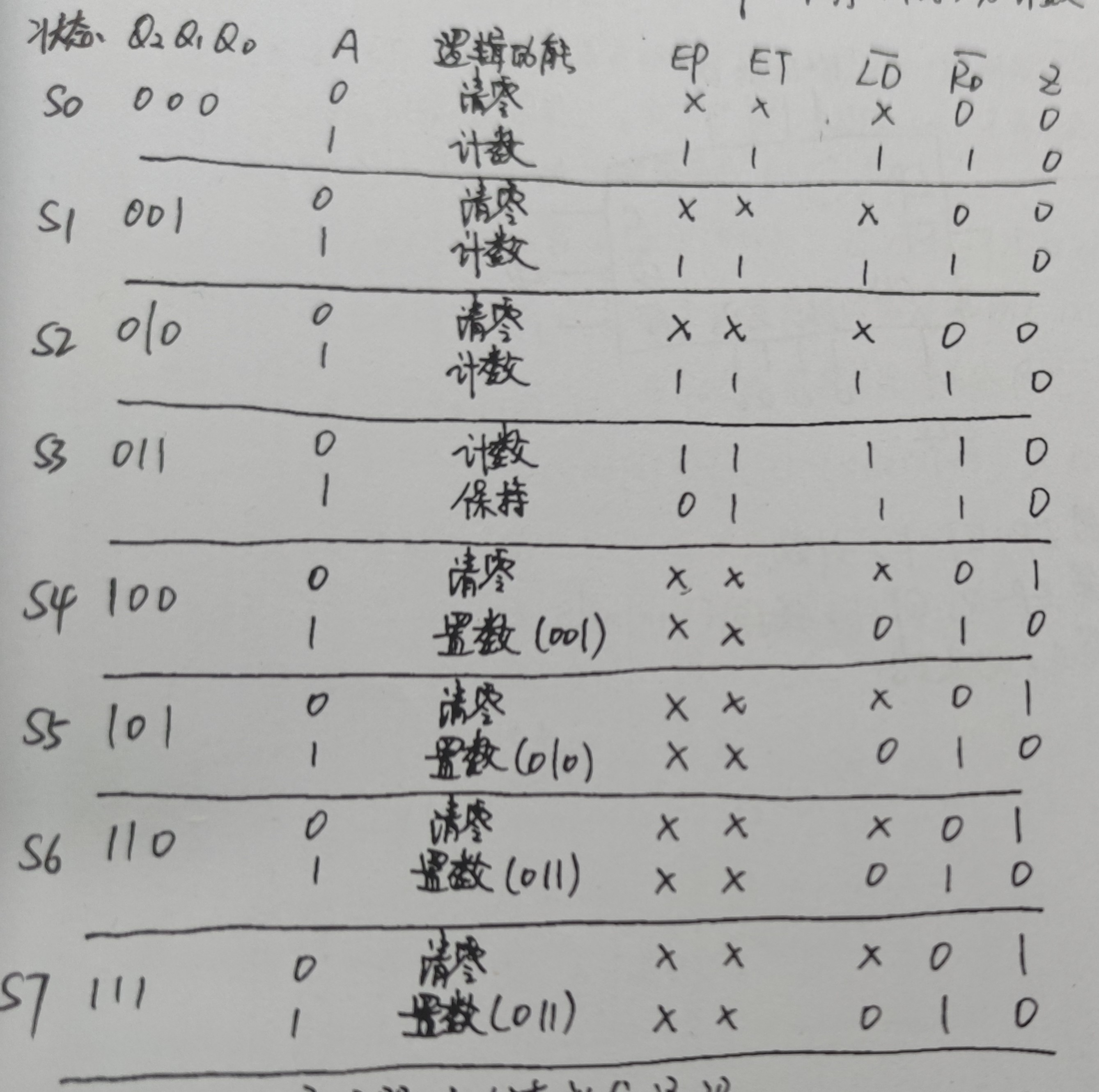

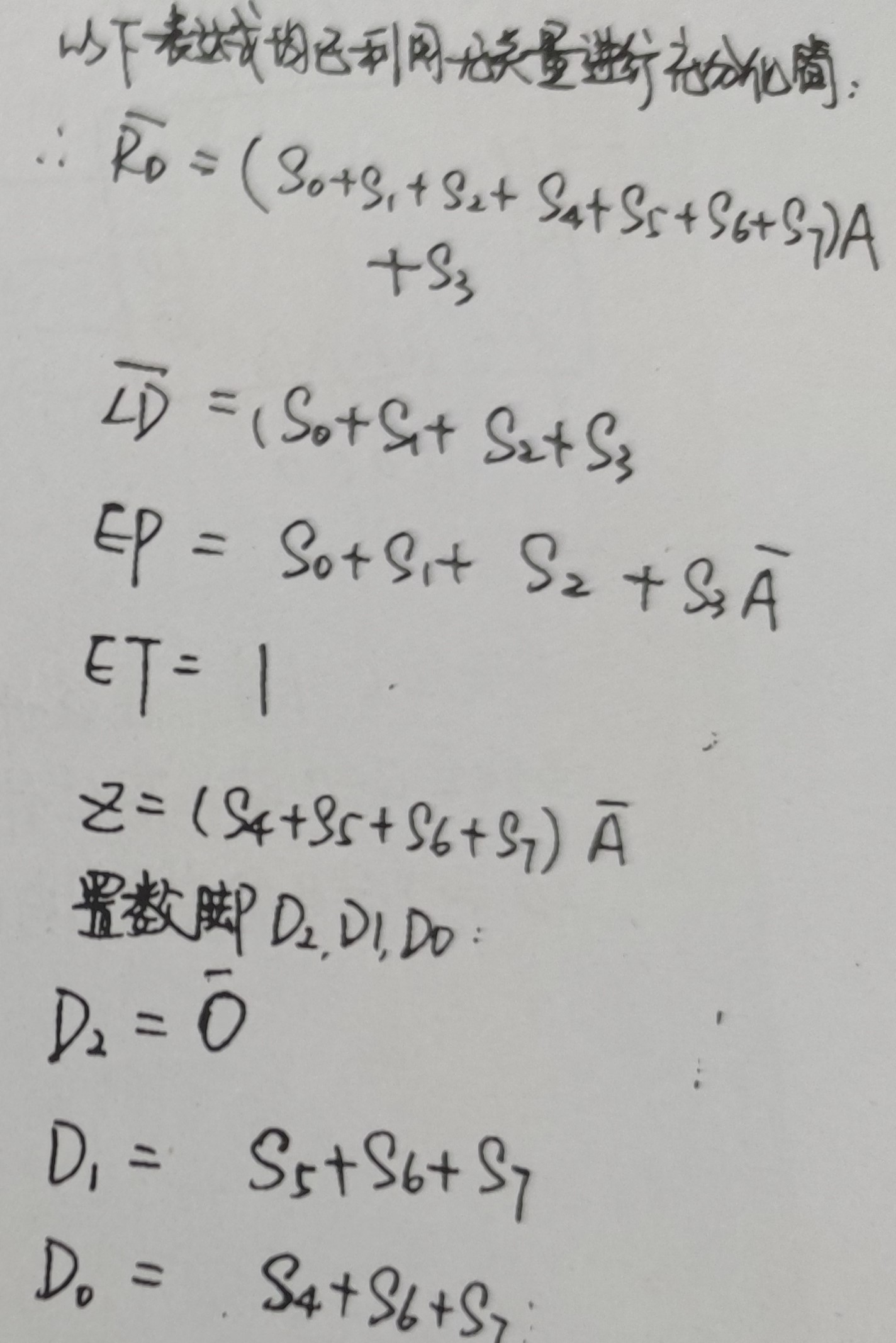

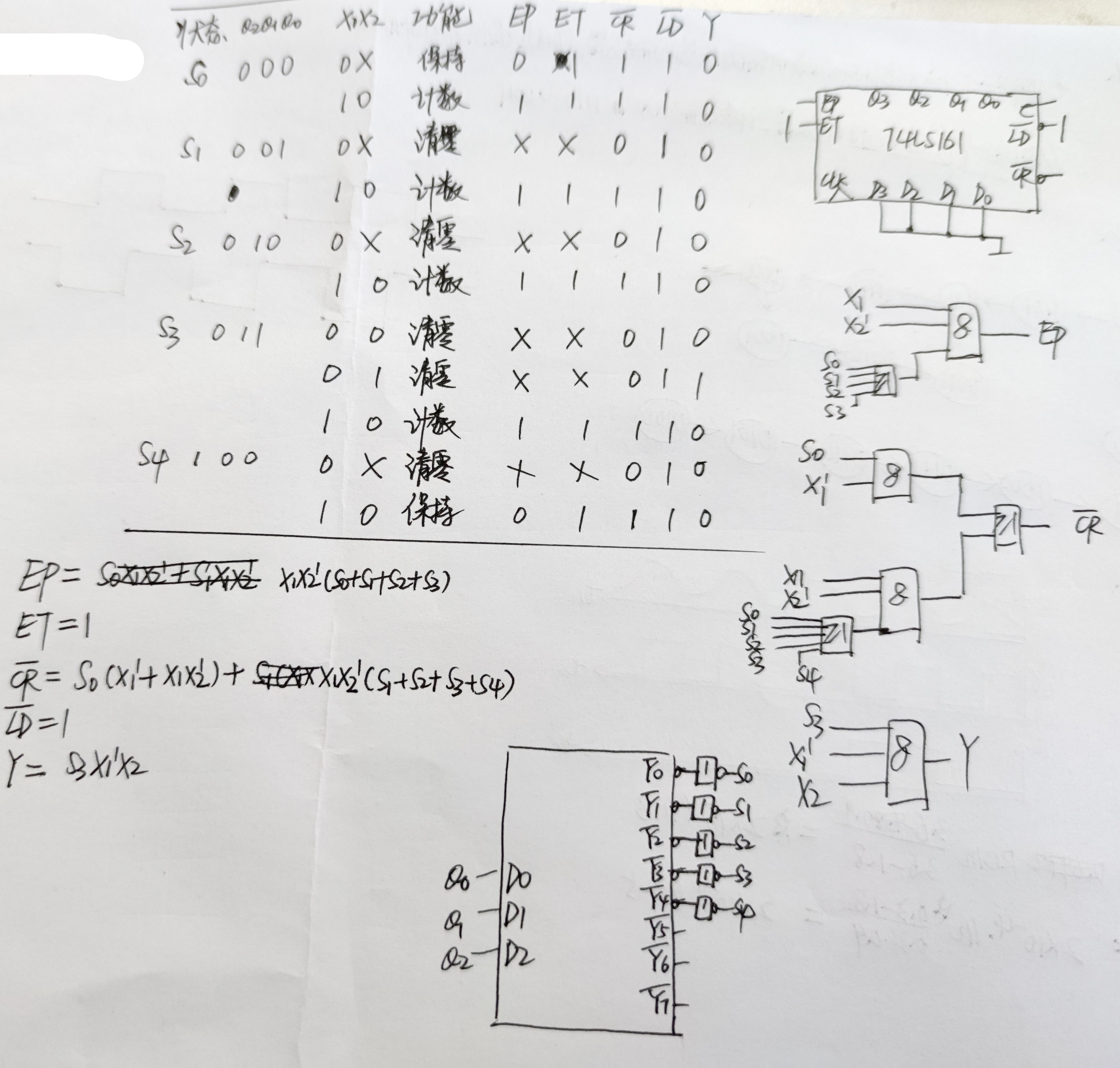

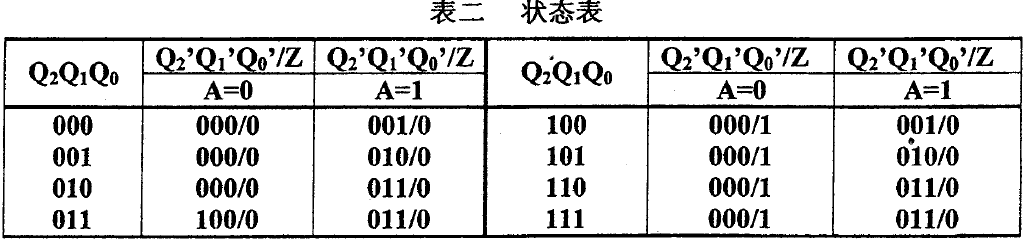

九、有一个外输入$A$及一个外输出$Z$的时序电路其状态表如下,用16进制同步计数器74LS161和必要的器件设计此时序电路。

解:

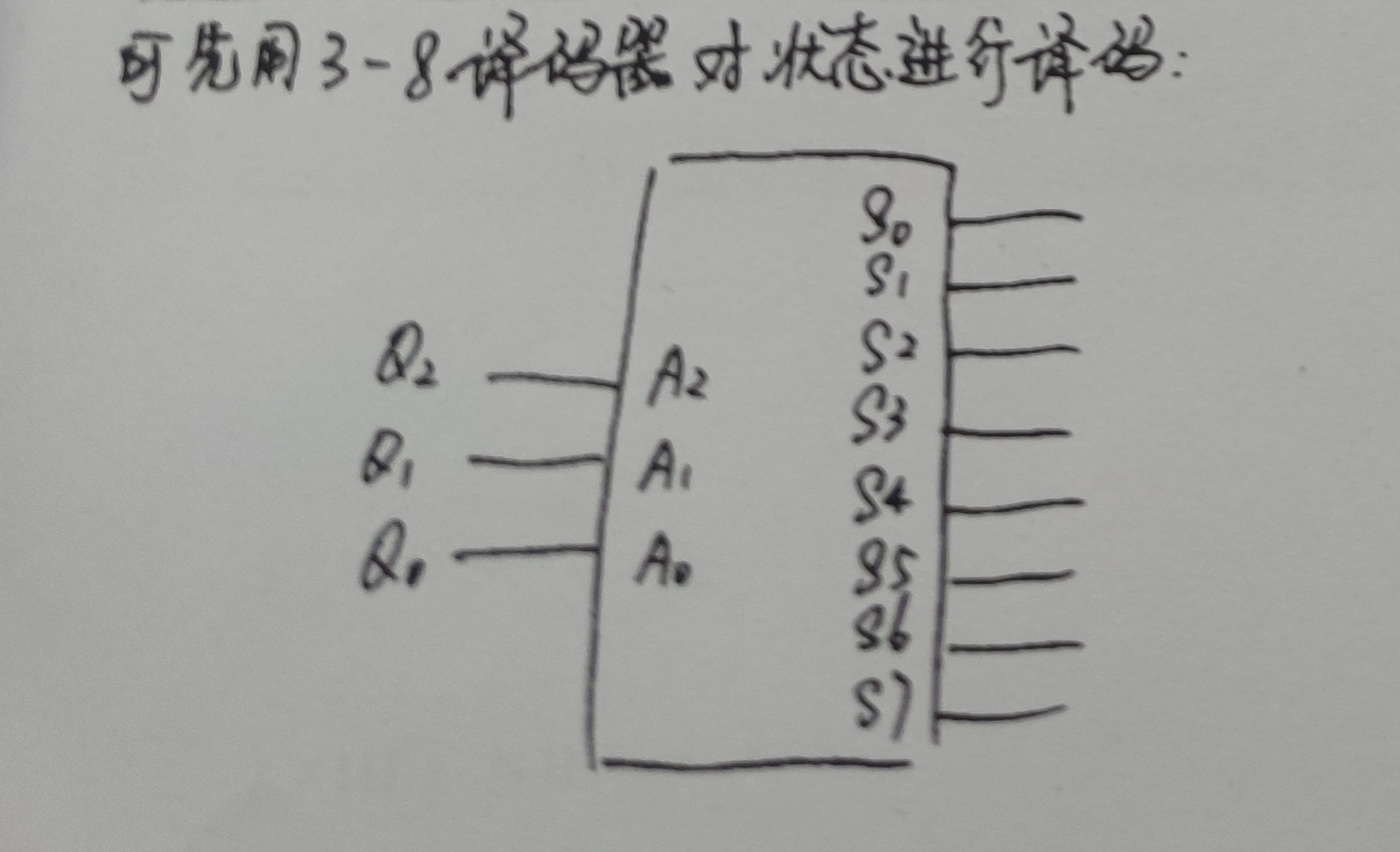

①. 对状态进行编码,并通过译码器解码。

②. 根据状态表写出每个状态转换对应在计数器上的操作(置数,清零,计数,保持)

③. 写出状态方程和输出方程

④. 画出电路图(省略)

思路:根据状态表灵活应用计数器的置数、清零、计数、保持功能。

12年真题

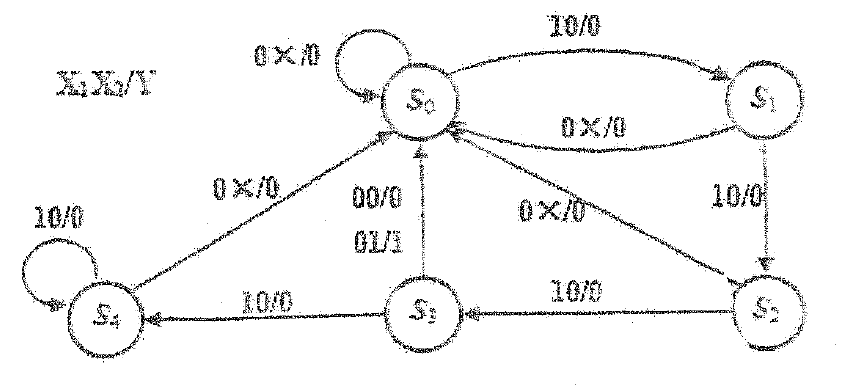

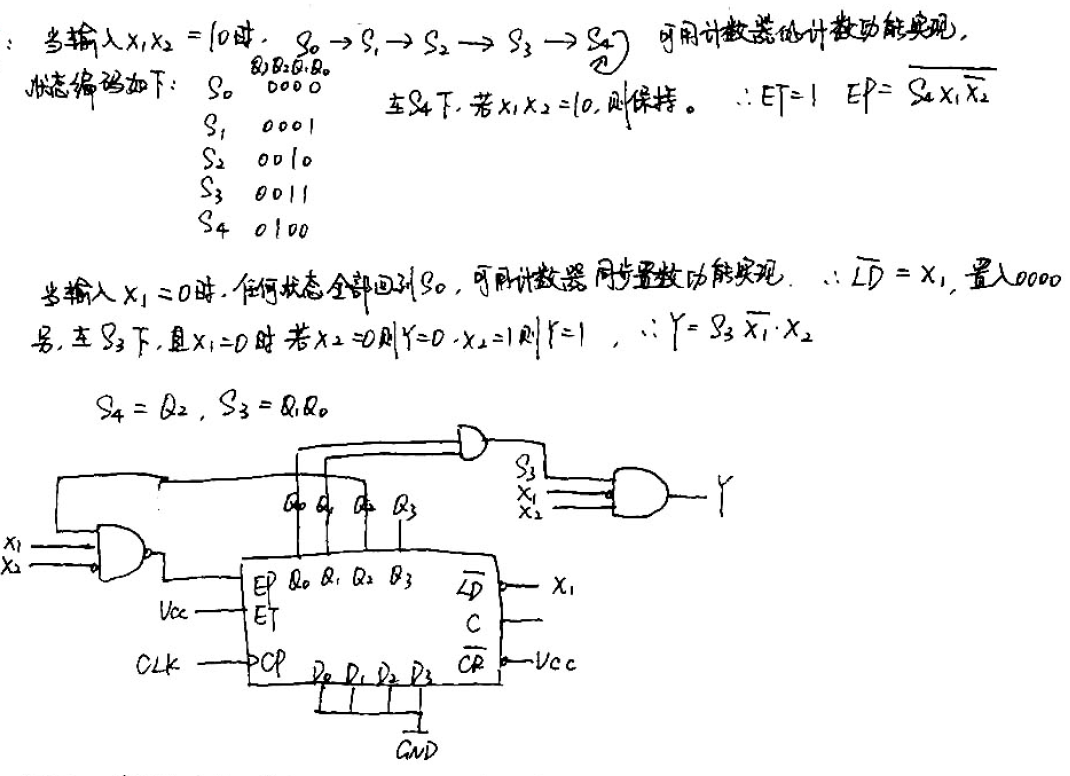

九、有一控制器状态图如下,其中$X_1X_2$是二个互斥的外输入,$Y$为外输出。用16进制同步加法计数器74LS161及其它必要的器件设计此控制器。

思路:对状态进行编码→判断状态图中每个状态变化过程对应的计数器操作→写状态表(包含计数器操作、$X_1X_2、EP、ET、\overline{CR}、\overline {LD}、Y$)→写出状态、输出方程→画电路图

用JK触发器设计时序电路

07年真题

十、用JK触发器和二选一数据选择器设计控制器时序电路。

思路:根据状态表写出状态方程和输出方程,再由状态方程得到激励方程。

当$A=0$时,

输出信号$Z=Q_2^n$。

当$A=1$时,

输出信号$Z=0$。

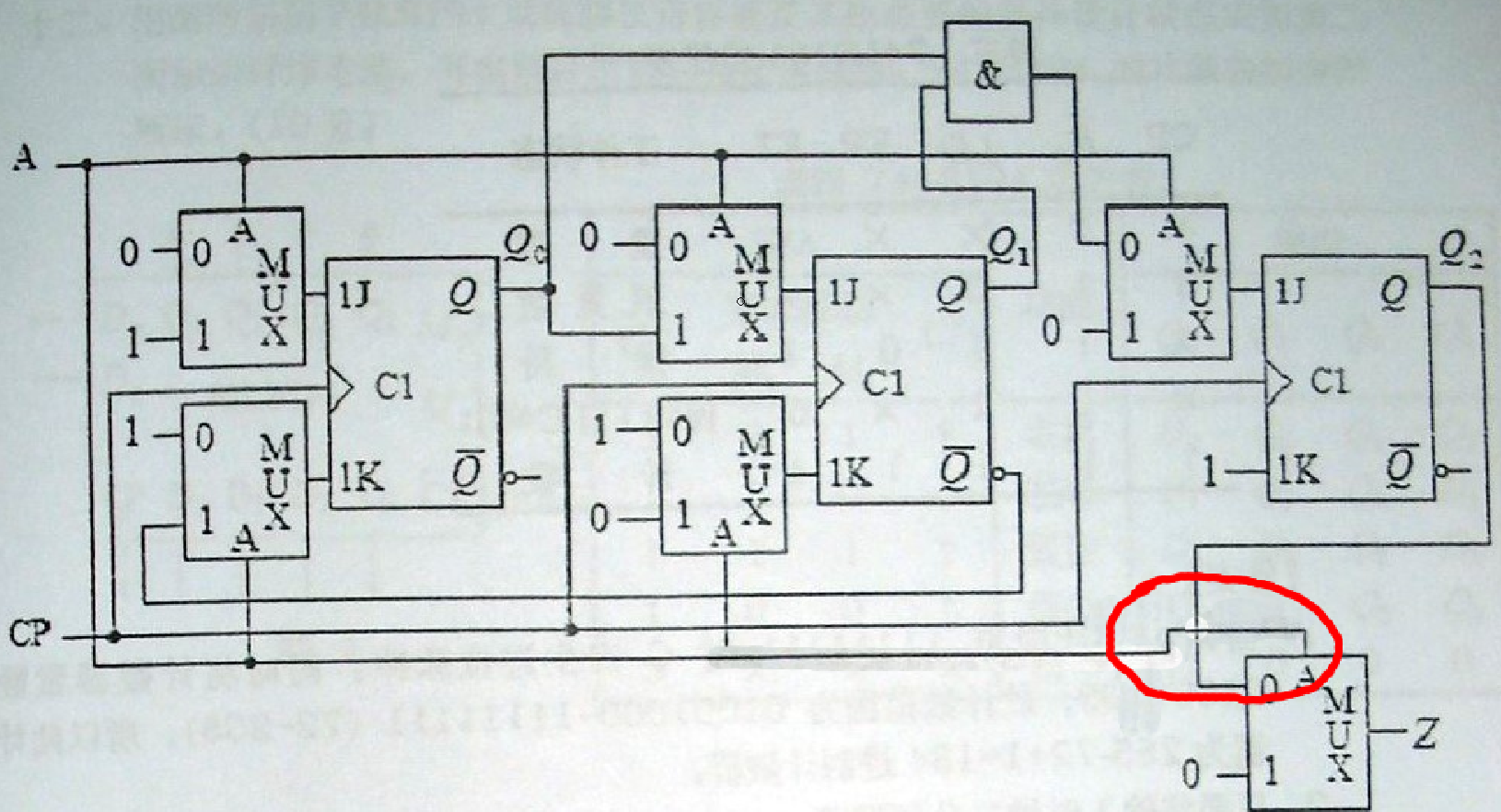

故电路图为:(答案在红圈处应该是有点错,在此修正)

10年真题

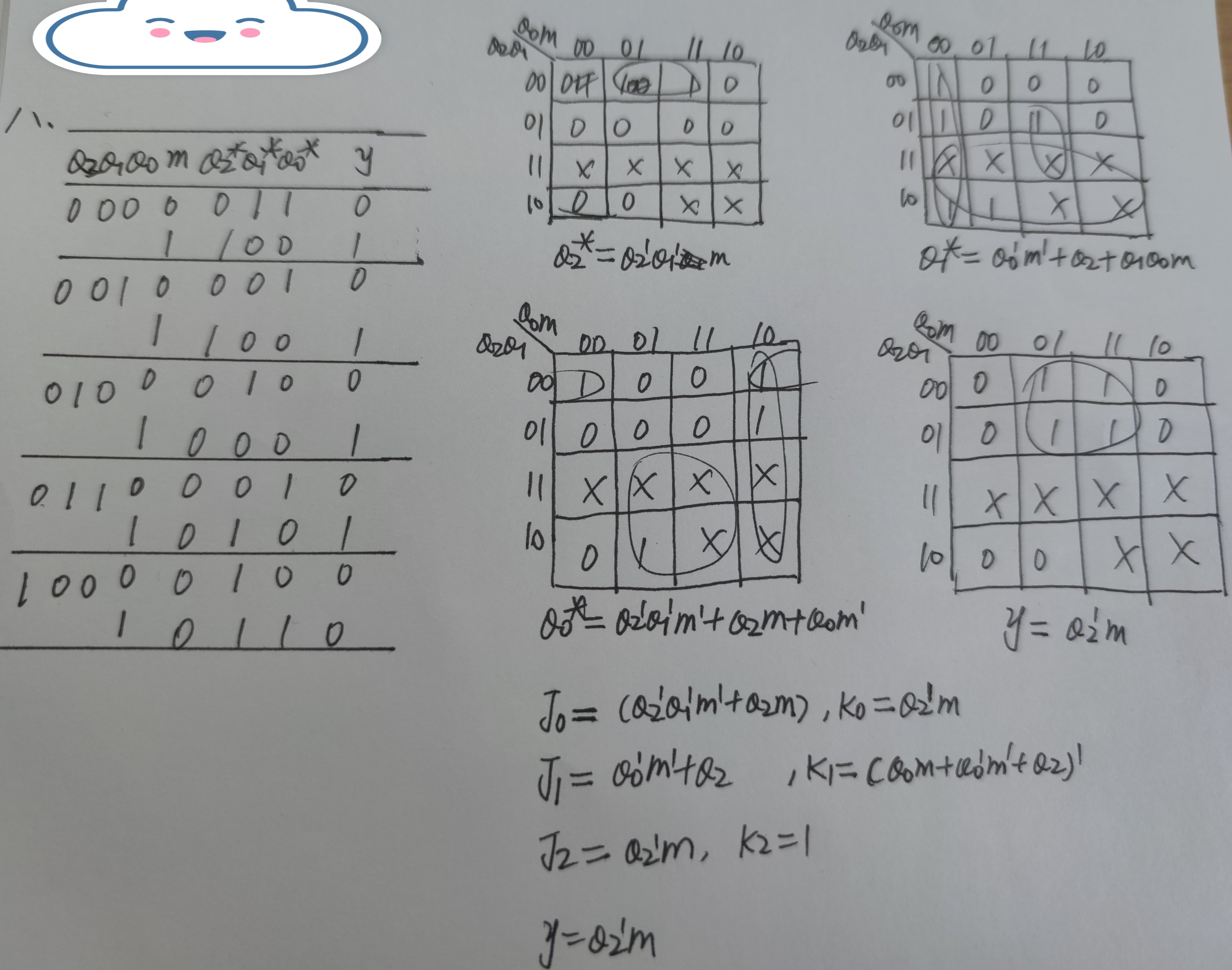

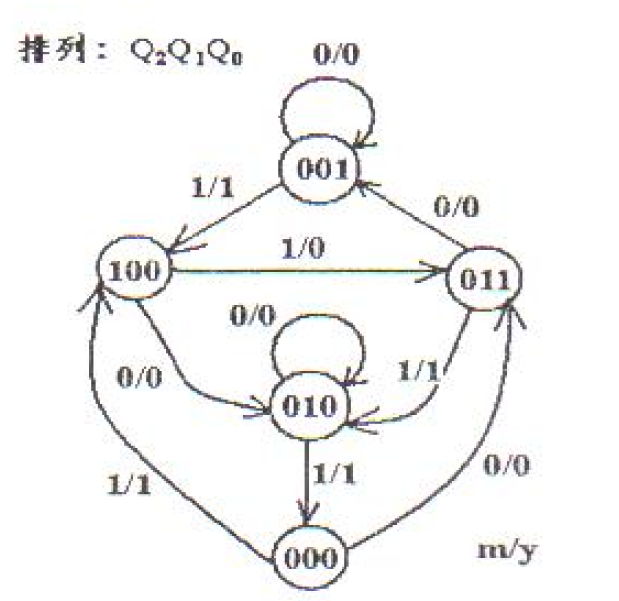

八、如下图所示是某同步时序电路的状态转换图,$m$为输入信号,$y$为输出信号,试用$JK$触发器及门电路设计此同步时序电路,要求写出次态卡诺图、激励方程、输出方程;画出逻辑电路图。

思路:根据状态转换图写出状态表→根据状态表列卡诺图→根据卡诺图写状态方程、输出方程、激励方程→画电路图。